Lecture 07 Introduction to the MIPS ISA

**University of Notre Dame**

#### CSE 30321 - Lecture 07 - Introduction to the MIPS ISA

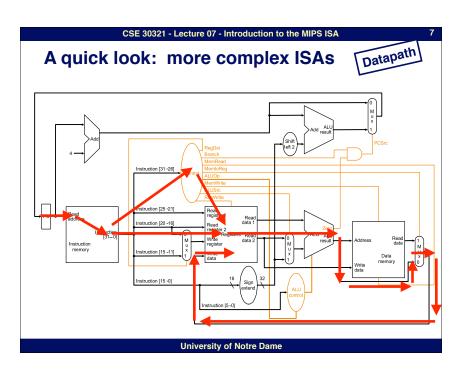

# **Motivation: Why MIPS?**

- Shortcomings of the simple processor

- Only 16 bits for data and instruction

- Data range can be too small

- Addressable memory is small

- Only support at most 16 instructions

- MIPS ISA: 32-bit RISC processor

- A representative RISC ISA

- (RISC Reduced Instruction Set Computer)

- A fixed-length, regularly encoded instruction set and uses a load/store data model

- Used by NEC, Cisco, Silicon Graphics, Sony, Nintendo

University of Notre Dame

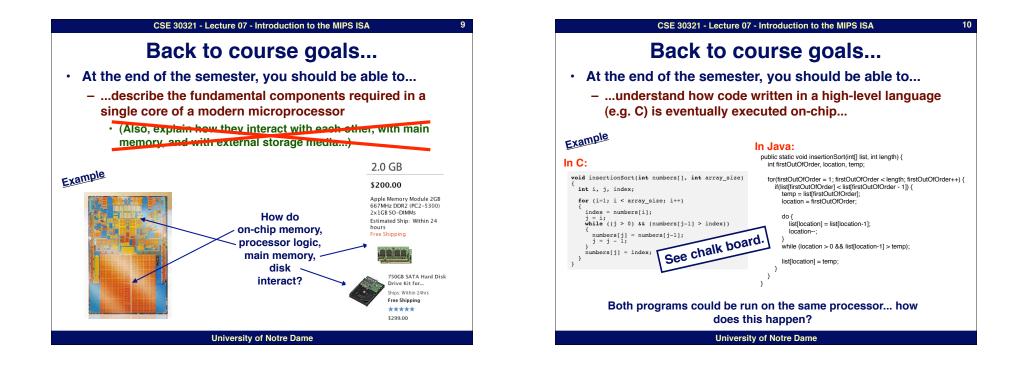

## In terms of course work:

- In class and in homework assignments, we look at design issues that relate to modern machines

- In labs, we apply these ideas on a smaller scale (i.e. the 6-instruction processor) and tie lessons learned in the lab back to class work

- Before we talk more about MIPS, let's spend a few slides thinking about how this fits into the big picture.

Use 30321 - Lecture 07 - Introduction to the MIPS ISA

12

We'll discuss MIPS more in a bit...

...but 1st, a few slides on ISAs in general.

## **Instructions Sets**

- "Instruction set architecture is the structure of a computer that a machine language programmer (or a compiler) must understand to write a correct (timing independent) program for that machine"

- IBM introducing 360 (1964)

- an instruction set specifies a processor's functionality

- what operations it supports

- what storage mechanisms it has & how they are accessed

- how the programmer/compiler communicates programs to processor

ISA = "interface" between HLL and HW

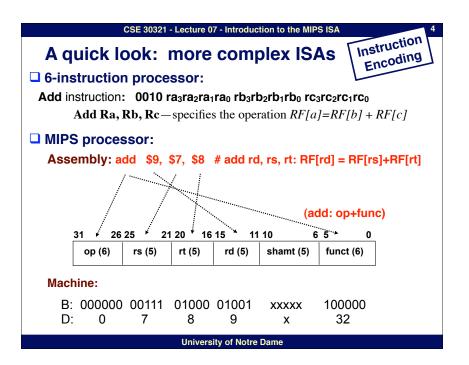

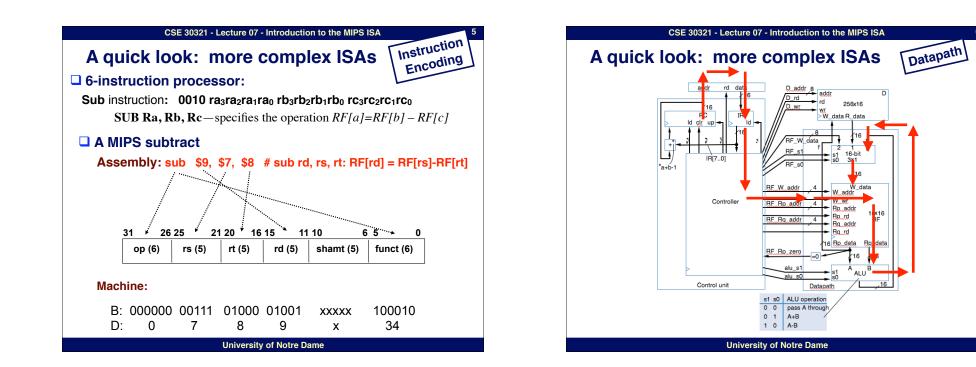

ISAs may have different sytnax (6-instruction vs. MIPS), but can still support the same general types of operations (i.e. Reg-Reg)

University of Notre Dame

#### CSE 30321 - Lecture 07 - Introduction to the MIPS ISA

# Instruction Set Architecture

- Must have instructions that

- Access memory (read and write)

- Perform ALU operations (add, multiply, etc.)

- Implement control flow (jump, branch, etc.)

- I.e. to take you back to the beginning of a loop

- Largest difference is in accessing memory

- Operand location

- · (stack, memory, register)

- Addressing modes

- · (computing memory addresses)

- (Let's digress on the board and preview how MIPS does a load)

- (Compare to 6-instruction processor?)

University of Notre Dame

#### CSE 30321 - Lecture 07 - Introduction to the MIPS ISA

# What makes a good instruction set

- implementability

- supports a (performance/cost) range of implementations

- implies support for high performance implementations

- programmability

- A bit more on this one...

- easy to express programs (for human and/or compiler)

- backward/forward compatibility

- implementability & programmability across generations

- e.g., x86 generations: 8086, 286, 386, 486, Pentium, Pentium II, Pentium III, Pentium 4...

- think about these issues as we discuss aspects of ISAs

#### CSE 30321 - Lecture 07 - Introduction to the MIPS ISA

# Programmability

- a history of programmability

- pre 1975: most code was hand-assembled

- 1975 1985: most code was compiled

- but people thought that hand-assembled code was superior

- 1985 present: most code was compiled

- and compiled code was at least as good as hand-assembly

over time, a big shift in what "programmability" means

# **Today's Semantic Gap**

- popular argument: today's ISAs are targeted to one HLL, and it just so happens that this HLL (C) is very low-level (assembly++)

- i.e. i = j + k; vs. Add Ri, Rj, Rk

- would ISAs be different if Java was dominant?

- more object oriented?

- support for garbage collection (GC)?

- support for bounds-checking?

- security support?

University of Notre Dame

#### CSE 30321 - Lecture 07 - Introduction to the MIPS ISA

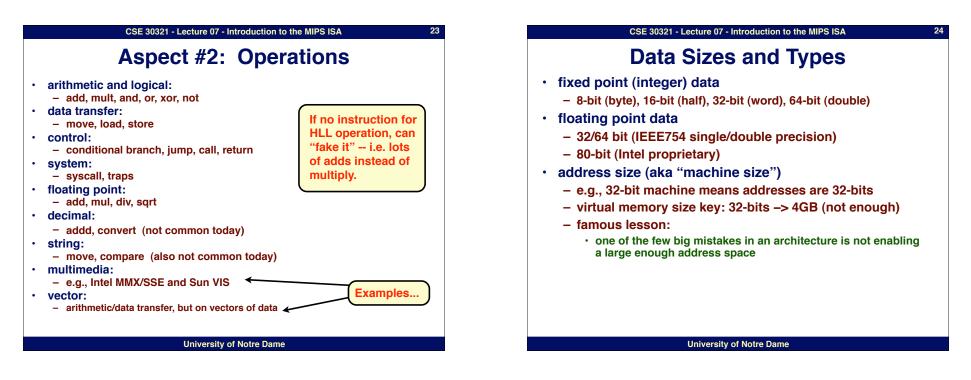

# **Instruction Set Aspects**

- #1 format

- length, encoding

- #2 operations

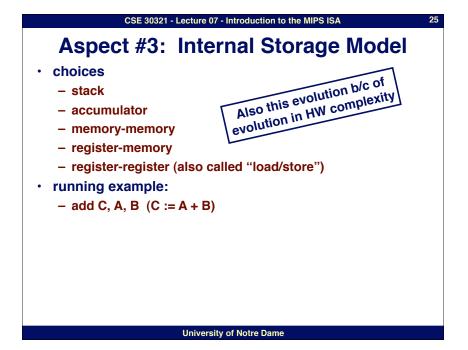

- operations, data types, number & kind of operands

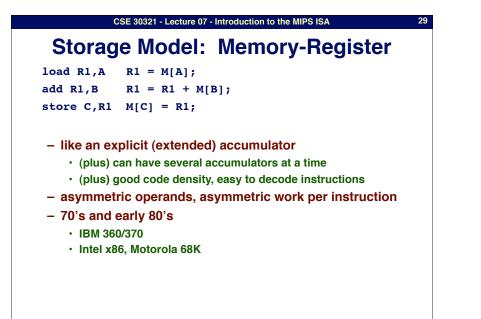

- #3 storage

- internal: accumulator, stack, general-purpose register

- memory: address size, addressing modes, alignments

- #4 control

- branch conditions, special support for procedures, predication

University of Notre Dame

#### CSE 30321 - Lecture 07 - Introduction to the MIPS ISA

# Aspect #1: Instruction Format

- fixed length (most common: 32-bits)

- (plus) easy for pipelining (e.g. overlap) and for multiple issue (superscalar)

- don't have to decode current instruction to find next instruction

- (minus) not compact

- Does the MIPS add "waste" bits?

- variable length

- (plus) more compact

- (minus) hard (but do-able) to superscalarize/pipeline

- PC = PC + ???

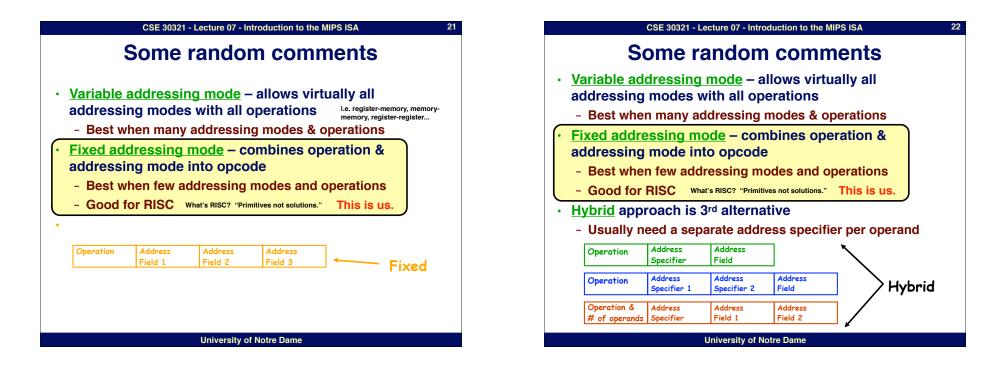

# CSE 30321 - Lecture 07 - Introduction to the MIPS ISA Variable Addressing Mode

20

# <u>Variable addressing mode</u> – allows virtually all

- addressing modes with all operations

- Best when many addressing modes & operations

| •             |             |         |                 | Variabl | le |

|---------------|-------------|---------|-----------------|---------|----|

| Operation &   | Address     | Address | Address         | Address |    |

| # of operands | Specifier 1 | Field 1 | <br>Specifier n | Field n |    |

i.e. register-memory, memory-memory, register-register... all possible

#### CSE 30321 - Lecture 07 - Introduction to the MIPS ISA **Storage Model: Stack** push A S[++TOS] = M[A];push B S[++TOS] = M[B];add T1=S[TOS--]; T2=S[TOS--]; S[++TOS]=T1+T2;M[C] = S[TOS - -];pop C operands implicitly on top-of-stack (TOS) - ALU operations have zero explicit operands (plus) code density (top of stack implicit) (minus) memory, pipelining bottlenecks (why?) - mostly 1960's & 70's x86 uses stack model for FP - (bad backward compatibility problem) JAVA bytecodes also use stack model

University of Notre Dame

CSE 30321 - Lecture 07 - Introduction to the MIPS ISA

# Storage Model: Accumulator

load A accum = M[A]; add B accum += M[B]; store C M[C] = accum;

- acc is implicit destination/source in all instructions

- ALU operations have one operand

- · (plus) less hardware, better code density (acc implicit)

- (minus) memory bottleneck

- mostly pre-1960's

- · examples: UNIVAC, CRAY

- x86 (IA32) uses extended accumulator for integer code

#### CSE 30321 - Lecture 07 - Introduction to the MIPS ISA

28

# Storage Model: Memory-Memory

add C,A,B M[C] = M[A] + M[B];

- no registers

27

- · (plus) best code density (most compact)

- Why? Total # of instructions smaller for one...

- + (minus) large variations in instruction lengths

- (minus) large variations in work per-instruction

- (minus) memory bottleneck

- no current machines support memory-memory

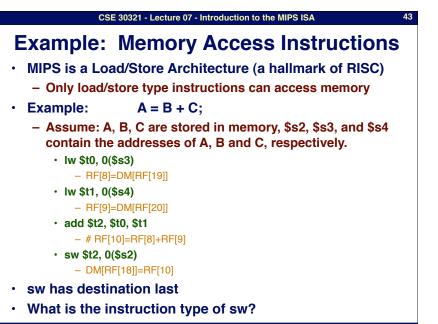

### Storage Model: Register-Register (Ld/St)

| load R1,A    | R1 = M[A];    |  |  |

|--------------|---------------|--|--|

| load R2,B    | R2 = M[B];    |  |  |

| add R3,R1,R2 | R3 = R1 + R2; |  |  |

| store C,R3   | M[C] = R3;    |  |  |

- load/store architecture: ALU operations on regs only

- (minus) poor code density

- (plus) easy decoding, operand symmetry

- (plus) deterministic length ALU operations

- · (plus) fast decoding helps pipelining and superscalar

- 1960's and onwards

- RISC machines: Alpha, MIPS, PowerPC (but also Cray)

University of Notre Dame

#### University of Notre Dame

# CSE 30321 - Lecture 07 - Introduction to the MIPS ISA 31 CSE 30321 - Lecture On to MIPS MIPS is a register-register machine 32x32-bit GPRs (General purp • Aside from enhancements we made, 6-instruction is too! 32x32-bit GPRs (General purp \$0 = \$zero (therefore only \$1 = \$at (reserved for associated or stated or

#### 32 CSE 30321 - Lecture 07 - Introduction to the MIPS ISA MIPS Registers (R2000/R3000) 32 bits □ 32x32-bit GPRs (General purpose registers) \$0 = \$zero (therefore only 31 GPRs) r<sub>o</sub> 0 r<sub>1</sub> \$1 = \$at (reserved for assembler) ... \$2 - \$3 = \$v0 - \$v1 (return values) \$4 - \$7 = \$a0 - \$a3 (arguments) **r**<sub>31</sub> b<sub>n-1</sub> ... b₀ PC \$8 - \$15 = \$t0 - \$t7 (temporaries) н \$16 - \$23 = \$s0 - \$s7 (saved) LO \$24 - \$25 = \$t8 - \$t9 (more temporaries) \$26 - \$27 = \$k0 - \$k1 (reserved for OS) \$28 = \$gp (global pointer) 32x32-bit floating point

- registers (paired double precision) • HI, LO, PC

- Status, Cause, BadVAddr, EPC

35

#### CSE 30321 - Lecture 07 - Introduction to the MIPS ISA

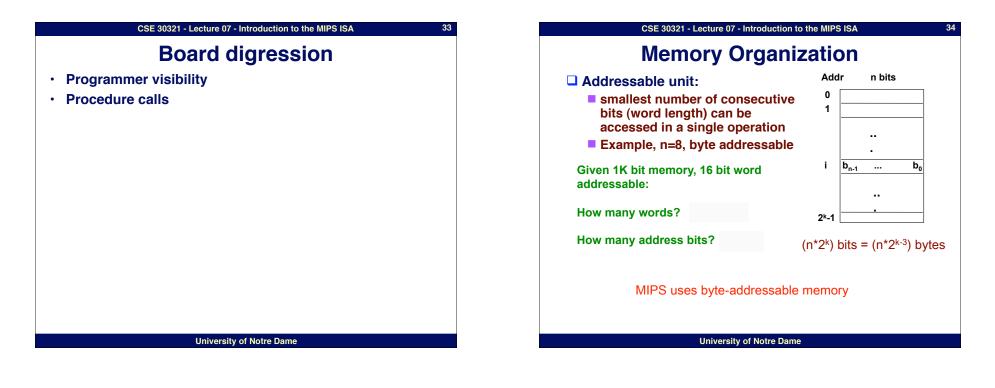

# Effect of Byte Addressing

MIPS: Most data items are contained in *words*, a word is 32 bits or 4 bytes. *Registers hold 32 bits of data*

- □ 2<sup>32</sup> bytes with byte addresses from 0 to 2<sup>32</sup>-1

- □ 2<sup>30</sup> words with byte addresses 0, 4, 8, ... 2<sup>32</sup>-4

- □ Words are aligned

- What are the least 2 significant bits of a word address?

#### CSE 30321 - Lecture 07 - Introduction to the MIPS ISA

36

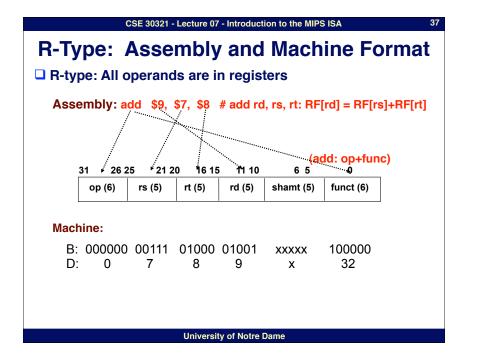

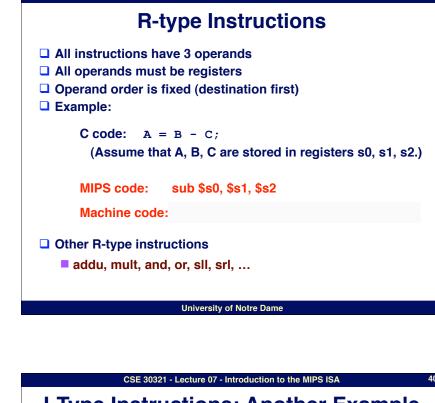

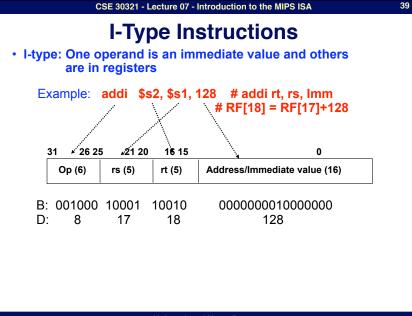

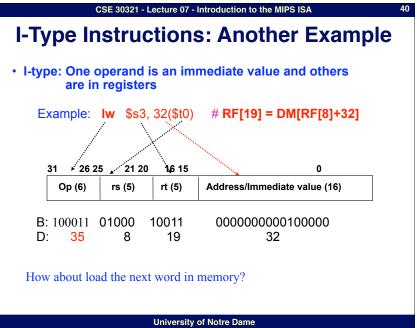

# A View from 10 Feet Above

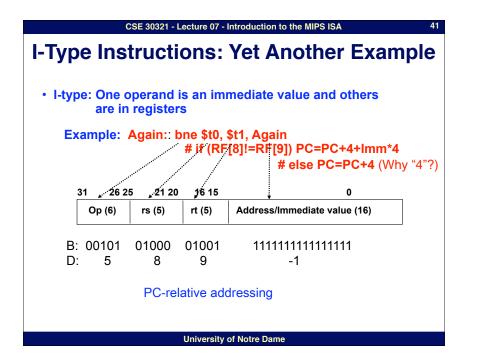

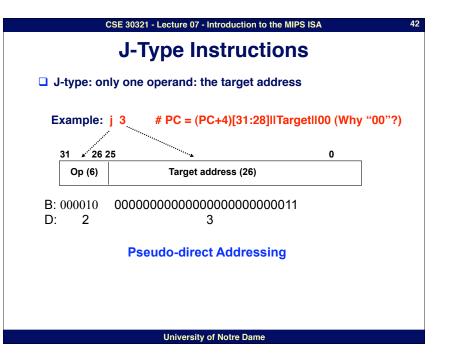

- Instructions are characterized into basic types

- Each type interpret a 32-bit instruction differently

- 3 types of instructions:

- R type

- I type

- J type

- Look at both assembly and machine code

- · In other words:

- As seen with Add, instruction encoding broken down into X different fields

- With MIPS, only 3 ways X # of bits arranged

- Think about datapath: Why might this be good?